XIPHEENS

Extended Integrated Processor for Hardware Emulation of Evolvable Neural Spiking Systems

The XIPHEENS project main purpose is to proof the industrial suitability of a HEENS-based ASIC (Application-Specific Integrated Circuit) executing a large-scale SNN operating in a multi-chip ring configuration. We target to rise the TRL of the HEENS technology from 4 to 6, seeking to confirm the innovation potential of this technology and to improve the capability to transfer it to industry.

Objectives

- To design, fabricate, and package an initial (slave) ASIC in 28nm CMOS technology, embedding a 4x4 PE array. The ASIC will be fully-functional as a slave node.

- To design, fabricate and package a final (slave) ASIC. It will embed a 16x16 PE array nodes, run at a higher frequency, include an external SPI input for sensors and real-time monitoring. The master will still be on an FPGA due to the project development time constraint.

- To test the ASICs and to evaluate the industrial benefit of the proposed system in terms of cost, performance and power consumption.

- To build and test a demonstrator based on a ring of chips. Final ASIC instances will be connected in a ring topology, including at least three chips, capable to emulate almost 25000 neurons executing SNN benchmarks.

- To evaluate the best valuation alternative. Registering a patent of the chip, creating a spinoff, or both, will be studied in the light of the obtained results.

- To acquire deep know-how and to train staff in advanced ASIC digital design.

nanoHEENS

This first prototype chip is capable of emulating 128 neurons and ~6K synapses in real time, with limited evolvable and monitoring capabilities.

|

nanoHEENS |

Processing Element Details |

nanoHEENS Technical Details

XIPHEENS

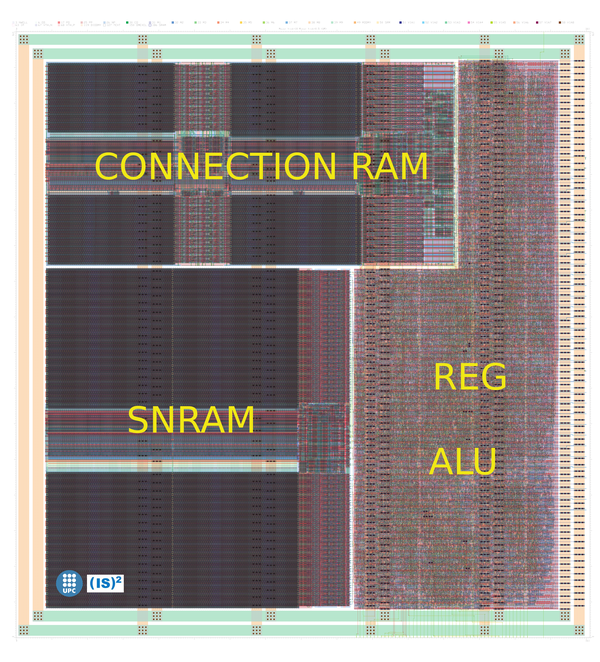

This ASIC is at the limit of the architecture, including 256 PEs capable of emulating 2048 neurons and close to 100K synapses in real time. Characterization is underway.

|

XIPHEENS |

XIPHEENS Wirebonding |

Physical Features

-

-

- Chip area 3.2 × 3.4 mm2

- Package size 2.4 × 2.5 cm2

- Max. clk frequency 500 MHz

- Power consumption 1.5 W @500 MHz

- Core voltage 0.9 V

- Pads voltage 1.8 V

- Max. out pin current 12 mA

-

Functional Features

-

-

- Multi-neural model support: LIF, QLIF, Izhikevich, custom, and any combination

- Synapse local plasticity: Fixed, STDP, memristive and custom-defined

- Local and global synapses

- On-the-fly topology change, Controller driven

- Simple execution: Library of models, netlist definition and user-friendly software

- Simple SPI external sensor interface

-

Target Applications

-

-

- Real-time neural culture emulation for hybrid in vitro, in silico experimentation

- Biologically inspired signal modeling and neural dynamics emulation

- Adaptive pattern recognition using spike-based computational models

- Real-time sensory processing and event-driven perception tasks

- Embedded and autonomous systems requiring fast and reliable spike-based computation

-

Coordinators:

Jordi Madrenas (jordi.madrenas@upc.edu)

Share: